數(shù)字集成電路版圖設(shè)計 附錄與持續(xù)補充

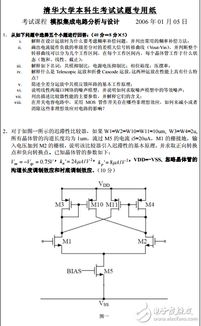

數(shù)字集成電路(IC)版圖設(shè)計是連接電路設(shè)計與物理實現(xiàn)的關(guān)鍵環(huán)節(jié),它將邏輯網(wǎng)表轉(zhuǎn)化為可在硅片上制造的幾何圖形。隨著工藝節(jié)點不斷演進,版圖設(shè)計的復(fù)雜性日益增加,附錄與持續(xù)補充成為學(xué)習(xí)和實踐中的重要部分。

一、附錄的核心價值

附錄通常包含以下關(guān)鍵內(nèi)容:

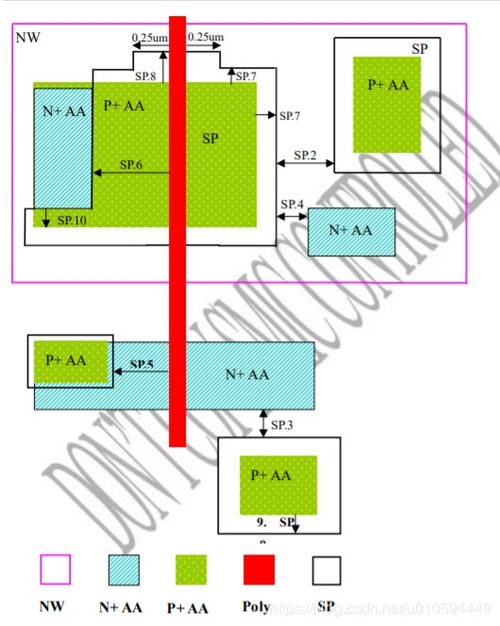

- 工藝設(shè)計規(guī)則(Design Rules):詳細列出制造工藝對版圖層、間距、寬度等幾何參數(shù)的限制,確保設(shè)計的可制造性。

- 標(biāo)準(zhǔn)單元庫文檔:提供標(biāo)準(zhǔn)邏輯單元(如與門、觸發(fā)器)的版圖視圖、時序模型和功耗數(shù)據(jù),是自動化布局布線的基礎(chǔ)。

- 電氣規(guī)則檢查(ERC)與設(shè)計規(guī)則檢查(DRC)指南:解釋常見錯誤類型及解決方法,幫助設(shè)計者提前規(guī)避物理驗證失敗的風(fēng)險。

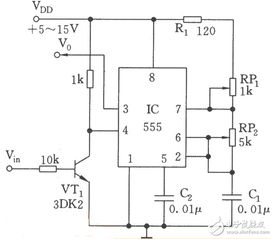

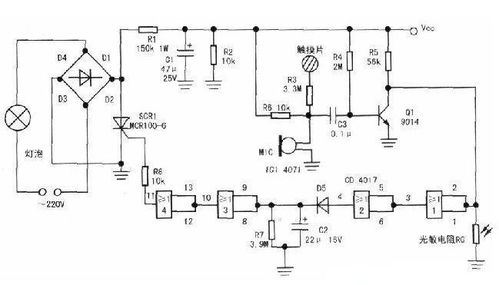

- 版圖與電路圖對應(yīng)表:輔助理解晶體管級電路與版圖幾何形狀的映射關(guān)系,尤其在定制設(shè)計(如模擬模塊)中至關(guān)重要。

二、持續(xù)補充的必要性

由于半導(dǎo)體技術(shù)快速迭代,版圖設(shè)計知識需不斷更新:

- 先進工藝挑戰(zhàn):在7納米及以下節(jié)點,量子效應(yīng)、寄生參數(shù)和工藝變異的影響顯著,需要補充針對性的版圖優(yōu)化技術(shù)(如多圖案分解、冗余通孔插入)。

- 工具演進:EDA工具(如Cadence、Synopsys平臺)的新功能與腳本使用方法需及時納入實踐指南。

- 新興設(shè)計范式:三維集成電路(3D-IC)、近似計算等新興領(lǐng)域?qū)Π鎴D提出了異構(gòu)集成、熱管理等新要求。

三、集成電路設(shè)計全流程中的版圖定位

版圖設(shè)計并非孤立環(huán)節(jié),需與前端設(shè)計協(xié)同:

- 邏輯綜合與版圖規(guī)劃:通過物理綜合工具預(yù)估布線擁塞和時序,提前調(diào)整模塊布局。

- 功耗完整性分析:補充電源網(wǎng)絡(luò)設(shè)計規(guī)則,避免IR壓降和電遷移導(dǎo)致的可靠性問題。

- 可制造性設(shè)計(DFM):引入基于模型的規(guī)則,如化學(xué)機械拋光(CMP)補償圖形,提升芯片良率。

四、實踐建議

- 建立知識庫:將項目經(jīng)驗(如天線效應(yīng)修復(fù)、 latch-up防護)整理為案例庫,形成可復(fù)用的附錄內(nèi)容。

- 動態(tài)更新機制:定期跟蹤晶圓廠技術(shù)文件更新、學(xué)術(shù)會議(如ISSCC)成果,迭代補充設(shè)計方法。

- 跨領(lǐng)域融合:關(guān)注封裝技術(shù)(如硅通孔TSV)對版圖的影響,拓展系統(tǒng)級視角。

###

數(shù)字集成電路版圖設(shè)計是工程與藝術(shù)的結(jié)合,附錄與持續(xù)補充既是技術(shù)文檔,也是設(shè)計智慧的沉淀。唯有通過系統(tǒng)化積累與動態(tài)演進,才能駕馭納米尺度下的設(shè)計挑戰(zhàn),最終實現(xiàn)高性能、高可靠性的芯片產(chǎn)品。

如若轉(zhuǎn)載,請注明出處:http://m.twax.cn/product/81.html

更新時間:2026-04-26 08:11:26